# Chapter 7

# Schottky Diode and Ohmic Contact

version 2.0 (updated: July 31, 2012), @Prentice Hall

#### Outline

- 7.1 The ideal Schottky diode

- 7.2 Ideal Schottky diode in thermal equilibrium

- 7.2.1 A simpler system: a metal-metal junction

- 7.2.2 Energy band lineup of metal-semiconductor junction

- 7.2.3 Electrostatics of metal-semiconductor junction in equilibrium

- 7.3 Current-voltage characteristics of the ideal Schottky diode

- 7.3.1 Electrostatics under bias

- 7.3.2 I-V characteristics: qualitative discussion

- 7.3.3 I-V characteristics: thermionic emission model

- 7.4 Charge-voltage characteristics of the ideal Schottky diode

- 7.5 Equivalent circuit models for the ideal Schottky diode

- 7.6 Non-ideal and second-order effects

- 7.6.1 Series resistance

- 7.6.2 Breakdown voltage

- 7.7 Integrated Schottky diode

- 7.8 Ohmic contacts

- 7.8.1 Lateral ohmic contact: transmission-line model

- 7.8.2 Boundary conditions imposed by ohmic contacts

- 7.9 Summary

- 7.10 Further reading

### Advanced Topics

- AT7.1 Non-ideal Schottky barrier height of metal-semiconductor junctions

- AT7.2 Drift-diffusion model for I-V characteristics

- AT7.3 Equivalent circuit model of Schottky diode for circuit design

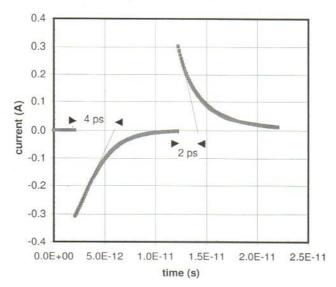

- AT7.4 Switching characteristics of Sthottky diode

#### Problems

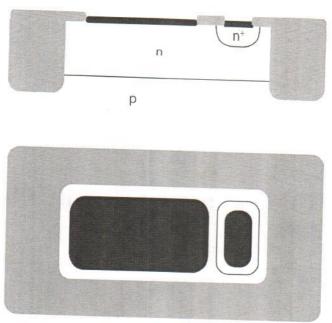

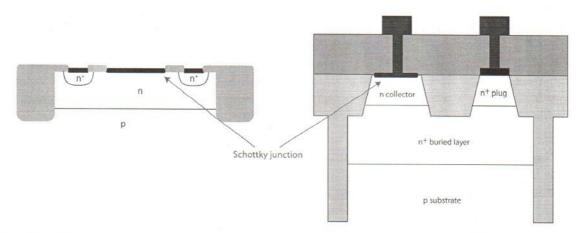

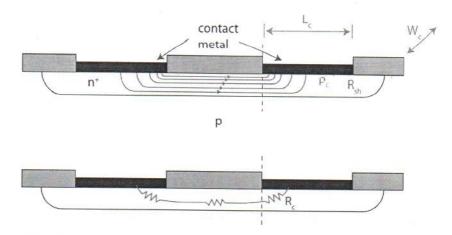

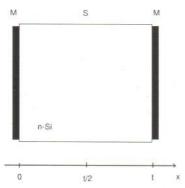

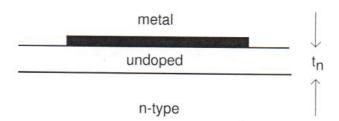

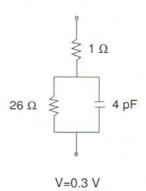

Figure 7.1: Cross section and top view of integrated Schottky diode.

This chapter is about the metal-semiconductor junction and two important applications: Schottky barrier diodes (or simply Schottky diodes) and ohmic contacts. Metal-semiconductor junctions are present in virtually all microelectronic devices. Their most pervasive form is ohmic contacts which are used to provide electrical access to devices from the outside world. However, under the right conditions, metal-semiconductor junctions can display rectifying behavior, just like PN junctions. This is exploited to make Schottky diodes. The uniqueness of the Schottky diode, in comparison with the PN diode, is its fast dynamic response. This arises from the fact that the Schottky diode is largely a majority-carrier-type device. Because of this, Schottky diodes have found use in many analog, digital, power and communications applications.

A top view and a cross-sectional view of an integrated Schottky diode is shown in Fig. 7.1. It consists of an n-type well on a p-type substrate. A metal layer is in direct contact with the n-well. If appropriately designed, this junction exhibits rectifying characteristics. The contact to the body is made through an n<sup>+</sup>region with a metal contact applied to it. The design here is optimized to make an ohmic contact that exhibits minimum contact resistance. One of the goals of this chapter is to understand when a metal-semiconductor junction shows rectifying characteristics and when it exhibits ohmic behavior. For the diode shown in this figure, the metal is referred to as the *anode* and the n-type semiconductor is the *cathode*. It is also possible to make metal/p-type Schottky diodes. In this case, the metal is the cathode and the p-type semiconductor is the anode.

This chapter studies in detail the physics of the metal-semiconductor junction and its use in Schottky diodes and ohmic contacts. It is organized as follows. We start by defining the notion of an "ideal Schottky diode." This is a hypothetical device of simplified geometry and physics that helps us focus on the most important issues. The metal-semiconductor junction in thermal

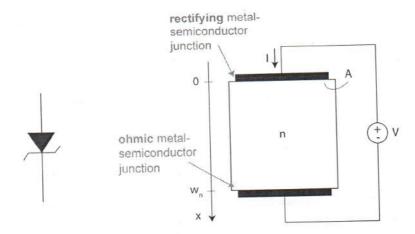

Figure 7.2: Left: circuit symbol of Schottky diode. Right: sketch of ideal Schottky diode.

equilibrium is discussed next. The treatment relies heavily on the energy band diagram view of semiconductors and metals. The consequences of applying a voltage to a Schottky diode are discussed next, first qualitatively and then quantitatively. We study both the current-voltage and the charge-voltage characteristics of Schottky diodes. We then discuss equivalent circuit models for Schottky diodes and some of the most significant non-ideal and second order effects. We devote a few pages to a few important technology and design issues in practical Schottky diodes. The chapter finishes with a detailed discussion of ohmic contacts, their physics and key design issues. A number of Advanced Topics at the end of the chapter allow the student to deepen understanding in several areas.

### 7.1 The ideal Schottky diode

We start this Chapter by defining the concept of an ideal Schottky diode. This is a device with simplified geometry and physics and no parasitics. The ideal Schottky diode captures the essence of the rectifying metal-semiconductor junction and hides some of its complexities. Later on in this chapter, we will relax some of the assumptions that we make here and we will also study the most significant non-idealities.

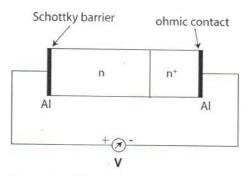

The circuit symbol and a sketch of an ideal Schottky diode are shown in Fig. 7.2. In this book, the ideal Schottky diode consists of an n-type semiconductor region with a Schottky metal on top (we use this term to refer to the metal of a metal-semiconductor junction that exhibits rectifying characteristics). The semiconductor is contacted by means of an ideal ohmic contact at the bottom. As a short-hand, when we simply talk about "the metal" in the context of a Schottky diode, we refer to the Schottky metal that yields the rectifying characteristics. The metal that makes the ohmic contact is usually referred to as "ohmic metal" or simply "contact."

In the analysis of the ideal Schottky diode, we are going to make the following assumptions:

All carrier flow is one dimensional. There are no 2D or 3D effects.

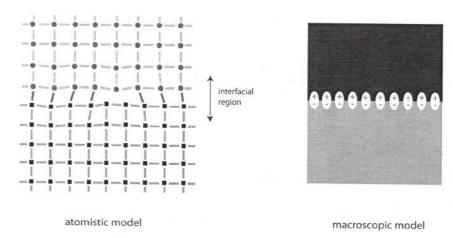

- The metal-semiconductor interface is smooth with ideal bonding for the semiconductor atoms preserved.

- The doping level in the semiconductor is uniform throughout.

- We assume that non-degenerate carrier statistics apply in all situations.

- We assume that the Schottky barrier height is given by the difference between the work function of the metal and the electron affinity of the semiconductor (for n-type semiconductor, this is explained below). This assumption is discussed in Sec. AT7.1.

- We assume that the alignment between metal and semiconductor work functions is such that in equilibrium, there is a depletion region on the semiconductor side.

- We treat the metal-semiconductor junction under the depletion approximation. We consider the rest of the semiconductor as quasi-neutral.

- We disregard the minority carriers and we therefore neglect generation and recombination.

- We ignore any resistance effects associated with the Schottky metal, the semiconductor or the ohmic contact (we study the impact of parasitic resistance in Sec. 7.6.1).

- $\bullet$  We assume ideal ohmic contact as defined in Sec. 5.2.2.

- We ignore any edge effects or other effects associated with the sidewalls of the device.

Fig. 7.2 defines the axis that we will use in our analysis of the Schottky diode. We place its origin at the metallurgical interface between the metal and the semiconductor. The extent of the semiconductor is  $w_n$ . The area of the device is A.

For a metal/n-semiconductor junction, such as the one depicted in Fig. 7.2, the voltage polarity is usually defined as in the figure. With this polarity, when V>0, the Schottky diode is in forward bias. When V<0, the Schottky diode is in reverse bias. The metal is the anode and the semiconductor is the cathode. Everything is reversed for a metal/p-semiconductor junction.

# 7.2 Ideal Schottky diode in thermal equilibrium

A metal-semiconductor junction is an artificial structure made out of two rather dissimilar materials. Whenever two materials with different properties are brought together in intimate contact, charge redistribution takes place. This has often fascinating consequences. The PN junction that was studied in the previous chapter was an example of this. The metal-semiconductor junction is unique in a number of ways. Before studying in detail the metal-semiconductor junction, a number of important concepts can be better grasped in a simpler metal-metal junction.

Figure 7.3: Energy band diagrams illustrating two different metals with different work functions: a) far apart from each other, b) just before contact is established, c) in intimate contact.

### 7.2.1 A simpler system: a metal-metal junction

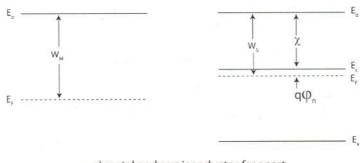

Fig. 7.3 illustrates the evolution of the electronic structure of two different metals as they are brought in contact to form a metal-metal junction. Fig. 7.3a) shows the energy band diagram of each metal when placed far apart from each other. Each metal has its own peculiar energy distribution of bands and bandgaps. The work functions (the minimum energy required to free up an electron) is also different in the two materials.

As the two metals are brought together, some electrons in the low work function metal, metal 2 on the right of Fig. 7.3, are presented with empty states at lower energy in the high work function metal 1 (Fig. 7.3b). As soon as contact is established, electrons from metal 2 rush to metal 1 to lower their energy. This makes metal 1 negatively charged and metal 2 positively charged. As time goes on and electron flow continues, an electric field builds up across the interface that in due time stops further electron migration. Equilibrium is eventually reached.

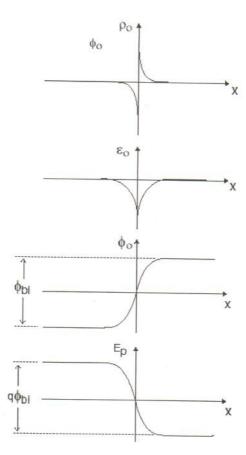

Figure 7.4: Volume charge density, electric field, electrostatic potential, and potential energy corresponding to the metal-metal junction of Fig. 7.3 in equilibrium.

This is a dynamic equilibrium situation. The initial tendency of electrons to flow from metal 2 to metal 1 in order to lower their energy is precisely counterbalanced by the electric field that gets set up at the interface. This electric field originates on the dipole of charge that is formed as a consequence of electron migration. This is graphed in Fig. 7.4. The electric field has a sign such that it opposes further electron transfer from metal 2 to metal 1. In Fig. 7.4,  $\mathcal{E}$  is negative as a consequence of the choice of axis. The electric field in turn results in a potential difference between the two materials that is called the built-in potential,  $\phi_{bi}$ . The potential energy associated with the electric field must be added to the energy band diagram. As a consequence, all the bands bend with a shape that is identical to the electrostatic potential with a minus sign (Fig. 7.3c).

When the two metals are sufficiently far apart, they can be considered as two different electronic systems with their own separate Fermi levels. The moment the two materials are brought in intimate contact and electrons are allowed to freely flow from one to the other, they constitute a new unified electronic system. In consequence, when thermal equilibrium is established, the Fermi level must be flat everywhere. This is the situation depicted in Fig. 7.3c).

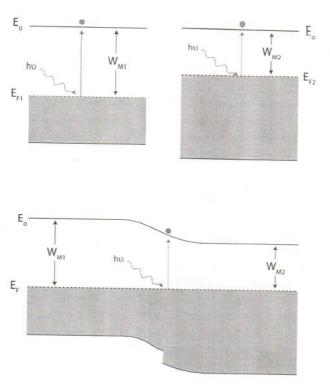

At this point it is legitimate to ask: what happens to the work function? How much energy does it take to extract an electron from the new combined electronic system? The best way to answer these questions is to carry out a fictitious photoelectric effect experiment, as sketched in Fig. 7.5. Suppose we have a tunable light source that can emit a spatially narrow beam of photons of any arbitrary energy. Suppose also that we have a way to detect when electrons are extracted from any one of the metals. If the beam of light has a narrow spatial spread, we can measure the *local work function* by shining light at a spot of the surface of the metal and observing the light energy at which electrons start escaping from that location.

When the two metals are apart, the energy required to free up an electron is well defined, i.e.,  $W_{M1}$  for metal 1 and  $W_{M2}$  for metal 2. When the metals are in contact the situation is not so clear. Sufficiently far away from the interface, each metal should not be aware of the presence of the other. Since the nature of each one has not been modified by bringing them into contact, it is then reasonable that the threshold light energy that frees up an electron remains unchanged. Far away from the interface, then, the work function of metal 1 is still  $W_{M1}$  and for metal 2 it is  $W_{M2}$ . As we approach the interface, electrons have migrated from metal 2 to metal 1. In consequence, the threshold photon-energy of metal 2 slowly increases as we approach metal 1, that is, we have to "dig deeper" into the electronic structure of metal 2 to find electrons that can be freed up. When we cross the interface into metal 1, previously empty electronic states are now full. As a result, the energy required to free up some of these electrons will be smaller than  $W_{M1}$ . As we go further and further away from the interface, the local work function approaches  $W_{M1}$ . This is sketched in Fig. 7.5.

We can then define, without any ambiguity, a local work function. We find that this parameter changes smoothly from one metal to the other and sufficiently far away from the interface it recovers the value that the metal exhibits when in isolation. It is clear that this local work function cannot change abruptly in space. If it did, electrons at the location where the discontinuity exists could move a small distance and easily lower their energy. This would not be an equilibrium situation.

Through the local work function, we can also define a local vacuum energy,  $E_o$  as in in Fig. 7.3. At any point in space,  $E_o$  is located at an energy above the Fermi level equal to the local work function. The shape of the local vacuum energy is identical to the potential energy of Fig. 7.4 and the total difference in energy of the local vacuum level across the structure is  $W_{M1} - W_{M2}$ . This allows us to conclude that the built-in potential of this structure is  $\phi_{bi} = (W_{M1} - W_{M2})/q$ .

A rigorous solution of the electrostatics of a metal-metal junction in thermal equilibrium, although not being very difficult to carry out, is of no great use to us. The one aspect of it that is important is the length scale of the space charge regions at the interface between the two metals. Because of the high electron density of a metal (about  $\sim 10^{22}~cm^{-3}$ ), a metal does not tolerate net charge in its bulk. If there is no overall charge neutrality in a metal, its net charge is confined to a thin sheet at the surface. In our case, this is the metal/metal interface. The space charge region at the interface is only a fraction of a nm thick, much smaller than all scale lengths of interest in microelectronic devices. For all purposes, it is then safe to consider this as a delta function and that is what we will do in this book.

We can now turn to the metal-semiconductor junction, the main topic of this chapter.

Figure 7.5: The photoelectric effect can be used to define a local work function in a metal-metal junction. Top: with the metals isolated, the threshold energy for extracting an electron is equal to the regular work functions  $W_{M1}$  and  $W_{M2}$ . Bottom: in a metal-metal junction, the local work function changes smoothly across the interface from  $W_{M1}$  to  $W_{M2}$ .

### 7.2.2 Energy band lineup of metal-semiconductor junction

A metal-semiconductor junction shares a lot of similarities with the metal-metal junction. While a metal is characterized by a partially full band, the most prominent feature of the energy band structure of a semiconductor is a complete band separated by a bandgap from the next empty band. Depending on the doping concentration and type of the semiconductor, the Fermi level can be located just about anywhere in the bandgap; it can even penetrate to some extent into the conduction or valence bands at high doping levels. In consequence, the detailed charge redistribution that takes place between a metal and a semiconductor when they are brought in intimate contact depends on the doping type and doping level of the semiconductor. So will the electrical properties of the resulting metal-semiconductor junctions.

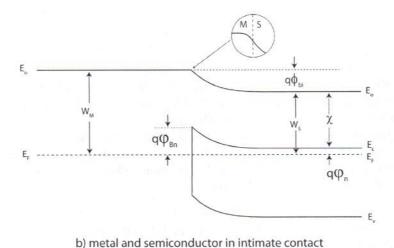

Fig. 7.6 shows the energy band diagram of a typical metal and a non-degenerate n-type semiconductor. As in a metal, a semiconductor is characterized by a work function  $W_S$ . In a semiconductor, the work function is defined as the energy difference between the vacuum level and the Fermi level in equilibrium. Because of this,  $W_S$  is a function of the doping level. In order to completely specify the relationship between the work function and the doping level in a semiconductor, an additional parameter is required. This is the electron affinity,  $\chi$ , which measures the energy difference between the vacuum level and the edge of the conduction band.  $\chi$

a) metal and semiconductor far apart

Figure 7.6: Energy band diagrams illustrating a metal and an n-type semiconductor: a) far apart from each other, b) in intimate contact.

is a property of the host semiconductor. For Si, for example,  $\chi = 4.04~eV$  at room temperature. The relationship between the electron affinity and the semiconductor work function is given by:

$$W_S = \chi + q\varphi_n \tag{7.1}$$

where  $q\varphi_n$  is the energy difference between  $E_c$  and  $E_F$  and is calculated from the doping level as discussed in Ch. 2.

Figure 7.6 illustrates a case in which the work function of the metal is higher than the work function of the semiconductor. This is the most typical situation for Si. In this instance, when the metal and the semiconductor are brought together, the difference in work functions results in electron redistribution in which electrons preferentially flow from the semiconductor to the metal. As in the metal-metal junction, this creates a charge dipole at the interface of the two materials. The semiconductor side becomes positively charged as a consequence of the exposed ionized donors, while the metal gets flooded by additional electrons and becomes negatively charged. The resulting energy band diagram in equilibrium is shown at the bottom of Fig. 7.6.

This energy band diagram is qualitatively identical to the one drawn in Fig. 7.3 for the metal-metal junction. Fundamental parameters of the semiconductor, such as  $\chi$  and  $E_g$ , are not affected by the presence of the metal. Additionally, sufficiently far away from the interface, the semiconductor and the metal are not upset by the presence of the junction. In consequence, their properties must remain the same as when they were isolated. For the semiconductor, that means that far away on the right,  $E_F$  is located at a distance  $W_S$  below the vacuum level and the energy difference between  $E_F$  and  $E_c$  is unchanged from the isolated case. In consequence, the built-in potential of this junction is given by:

$$\phi_{bi} = \frac{1}{q}(W_M - W_S) \tag{7.2}$$

What is substantially different in the case of the metal-semiconductor junction with respect to the metal-metal one is the relative band bending in the metal and the semiconductor. Since a metal has a carrier concentration several orders of magnitude higher than a semiconductor, the potential distribution across a metal-semiconductor junction is extremely asymmetric, with the semiconductor absorbing the great majority of it. The metal energy bands bend a negligible fraction of  $q\phi_{bi}$  over a very small distance from the interface. In contrast, the bands in the semiconductor bend up substantially over a much longer length scale. The closer we get to the interface, the further away the conduction band is from the Fermi level and the fewer electrons there are. The detailed shape of the band bending in the semiconductor will be calculated in the following section. We will see that it is nearly parabolic.

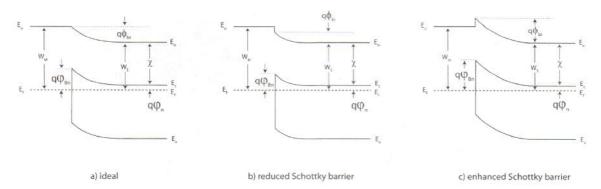

At the metal-semiconductor interface, an electron with an energy equal to the Fermi level has an abrupt barrier to overcome in order to get from the metal to the semiconductor. This energy barrier plays a crucial role in the operation of metal-semiconductor junctions out of equilibrium and is called the *Schottky barrier height*. From Fig. 7.6, it is easy to see that:

$$q\varphi_{Bn} = W_M - \chi \tag{7.3}$$

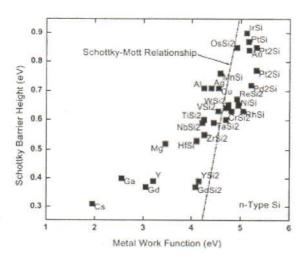

This equation says that the Schottky barrier height is a property of the metal-semiconductor pair and it is not a function of the doping level of the semiconductor. This is often referred to as the Schottky-Mott relation.

Combining Eqs. 7.3, 7.1 and 7.2, we obtain an expression for the built-in potential of a Schottky diode in terms of the Schottky barrier height:

$$q\phi_{bi} = q\varphi_{Bn} - q\varphi_n \tag{7.4}$$

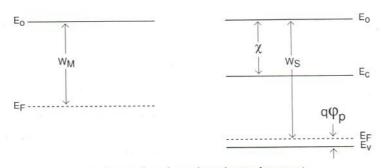

Fig. 7.7 shows the energy band diagram for a typical metal/p-semiconductor junction: With the two materials far apart, the Fermi level in the metal is higher than the Fermi level in the semiconductor. In this instance, as we bring the materials together, electrons flow from the metal to the semiconductor. On the metal side, this leads to a surface with a deficiency of electrons, that is, positively charged. Since the semiconductor is p-type, metal electrons rush to the semiconductor and preferentially occupy the holes at the top of the valence band. In

a) metal and semiconductor far apart

#### b) metal and semiconductor in intimate contact

Figure 7.7: Energy band diagrams illustrating a metal and an p-type semiconductor: a) far apart from each other, b) in intimate contact.

consequence, there are fewer holes there when equilibrium is established and the semiconductor becomes negatively charged.

In thermal equilibrium, the bands in the semiconductor bend down reflecting the reduction of holes on the semiconductor side as the interface is approached. There is also an energy barrier that appears at the metal-semiconductor interface. It is customary to refer to it as the Schottky barrier height for holes  $q\varphi_{Bp}$  (always a positive quantity). From the figure, we can see that  $q\varphi_{Bp}$  is given by:

$$q\varphi_{Bp} = \chi + E_g - W_M \tag{7.5}$$

This is also independent of doping. In terms of  $q\varphi_{Bp}$ ,  $\phi_{bi}$  is:

$$q\phi_{bi} = q\varphi_{Bp} - q\varphi_p \tag{7.6}$$

where  $q\varphi_p$  is the energy distance between  $E_F$  and  $E_v$ .

An interesting property of a metal-semiconductor pair is obtained by adding Eqs. 7.3 and 7.5:

$$q\varphi_{Bn} + q\varphi_{Bp} = E_g \tag{7.7}$$

The Schottky barrier heights of a metal on a semiconductor when p-type doped and n-type doped add up to the bandgap of the semiconductor. This is a handy relationship that can be exploited in practice if we are missing the Schottky barrier height for a certain metal-semiconductor pair but we have its value for the same system with the contrary polarity of the semiconductor.

Before we move on, it is important to note that Eqs. 7.3 and 7.5 should not be used to estimate the Schottky barrier height of a metal/semiconductor pair. These equation suggest that the Schottky barrier height is a fundamental property of the bulk materials involved. In practice, it is found that for a given metal-semiconductor pair,  $q\varphi_{Bn}$  and  $q\varphi_{Bp}$  depend on the details of the fabrication process and the crystalline orientation of the semiconductor. This strongly suggests that the Schottky barrier height is affected to some extent by the interfacial chemistry and is not just a property of the bulk materials. For many metals, the predictions of Eq. 7.3 can be significantly off. More details of this are given in Appendix AT7.1. The practical approach is not to rely on Eq. 7.3 or 7.5 but rather design experiments to measure the actual value of the Schottky barrier height of interest. Eqs. 7.4 and 7.6 remain correct and can be safely used to relate the built-in potential, the Schottky barrier height and the relative location of the Fermi level in the semiconductor. As is shown in Appendix AT7.1, Eq. 7.7 also remains correct.

In the next section, we study the electrostatics of the metal-semiconductor junction in thermal equilibrium in a more quantitative way.

## 7.2.3 Electrostatics of metal-semiconductor junction in equilibrium

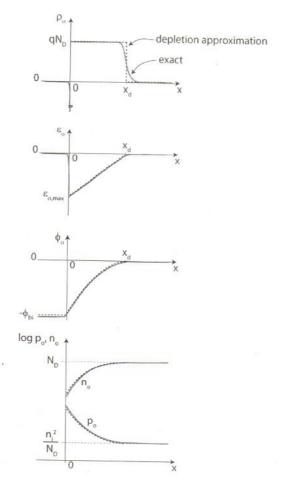

The goal of this section is to develop a first-order model for the electrostatics of a metal/semiconductor junction in thermal equilibrium, that is, to calculate the volume charge density, electric field, electrostatic potential and carrier concentration distributions in space across the structure. This understanding is essential to deal with situations out of equilibrium later on in this chapter. This section treats the metal/n-semiconductor junction. The procedure is similar to the metal/p-type semiconductor junction and leads to very similar equations.

The problem to be solved is a typical one in semiconductor devices and it resembles the PN diode. In most metal-semiconductor junctions, the net volume charge density in the semiconductor in the vicinity of the metal is high enough that it cannot be considered quasi-neutral any longer. Because of this, the region close to the metal-semiconductor interface is called the *space-charge region*, or SCR. Unlike the relatively gradual non-uniformly doped distributions that we studied in Ch. 4, a space charge region many times appears in regions in which abrupt transitions occur. It is the case, for example, in a PN junction and also that of a metal-oxide-semiconductor structure, as we will describe later on in this book. Sufficiently far away from the metal-semiconductor interface, in the bulk of the semiconductor, charge neutrality should prevail. This region is called the *quasi-neutral region* or QNR. The boundary between the SCR and the

QNR is fairly sharp.

The first step in thinking about the electrostatics of this problem is to consider the volume charge density,  $\rho_o$ . In general, for a metal/n-semiconductor junction, and in the absence of a substantial concentration of compensating acceptors,  $\rho_o$  is given by:

$$\rho_o = q(p_o - n_o + N_D) \tag{7.8}$$

Deep in the quasi-neutral bulk of the semiconductor  $\rho_o \simeq 0$ . As we advance towards the metal-semiconductor interface,  $n_o$  drops and  $p_o$  consequently rises (the  $n_o p_o$  product must remain constant in equilibrium). This makes  $\rho_o$  positive. Since  $p_o$  starts from an extremely small value in the QNR, the drop in  $n_0$  is most significant. If the built-in potential of the junction is not too small, as we get closer to the interface, we will reach a point in which  $n_o$  has become negligible in front of  $N_D$ . Similarly, if  $\phi_{bi}$  is not too high either,  $p_o$  might never become significant next to  $N_D$ . When all this happens,  $\rho_o \simeq qN_D$ . Because of the exponential dependence of  $n_o$  on  $\phi_o$ , the transition between  $\rho_o \simeq 0$  and  $\rho_o \simeq qN_D$  is actually quite sharp. This suggests a simple approximation to the charge distribution in the semiconductor:

$$\rho_o(x) \simeq qN_D \quad \text{in SCR: } 0 \le x < x_d$$

$$\rho_o(x) \simeq 0 \quad \text{in QNR: } x_d < x$$

(7.9)

$$\rho_o(x) \simeq 0 \quad \text{in QNR: } x_d < x$$

(7.10)

This assumption of a box-like shape for the charge distribution is the depletion approximation, something that we have already become familiar with in the analysis of the PN diode. Establishing the location of the boundary between the SCR and the QNR,  $x_d$  in Eqs. 7.9 and 7.10, is one of the goals of the calculations that follow. This charge distribution is shown in Fig. 7.8.

Integration of this volume space-charge density distribution yields the electric field profile:

$$\mathcal{E}_o(x) \simeq \frac{qN_D}{\epsilon}(x - x_d)$$

in SCR:  $0 \le x \le x_d$  (7.11)

$\mathcal{E}_o(x) \simeq 0$  in QNR:  $x_d \le x$  (7.12)

$$\mathcal{E}_o(x) \simeq 0 \qquad \text{in QNR: } x_d \leq x \qquad (7.12)$$

This field is negative because it points from the semiconductor into the metal, contrary to our choice of axis, as shown in Fig. 7.8.

One more integration yields the electrostatic potential:

$$\phi_o(x) = -\frac{qN_D}{2\epsilon}(x^2 - 2x_d x + x_d^2)$$

in SCR:  $0 \le x \le x_d$  (7.13)

$\phi_o(x) = 0$  in QNR:  $x_d \le x$  (7.14)

$$\phi_o(x) = 0 \qquad \text{in QNR: } x_d \le x \tag{7.14}$$

where we have selected  $\phi_o(bulk) = 0$  as the reference for potentials. The potential is also graphed in Fig. 7.8.

Figure 7.8: Volume charge density, electric field, electrostatic potential, and equilibrium carrier concentrations across metal/n-semiconductor junction.

The extension of the depletion region,  $x_d$ , is obtained by demanding that the total potential difference across the semiconductor be  $\phi_{bi}$  which we know from energy arguments (Eq. 7.4). With our selected potential reference, that implies that  $\phi_o(0) = -\phi_{bi}$ . Solving for  $x_d$  in Eq. 7.13, we get:

$$x_d = \sqrt{\frac{2\epsilon\phi_{bi}}{qN_D}} \tag{7.15}$$

The maximum electric field occurs at the interface and it is given by:

$$|\mathcal{E}_{o,max}| = \frac{qN_D x_d}{\epsilon} = \sqrt{\frac{2qN_D \phi_{bi}}{\epsilon}}$$

(7.16)

These two equation state that the higher the doping level, the thinner the depletion region is and the higher the electric field is at the metal/semiconductor interface. This is a consequence of the electrostatics of a charge dipole. To attain a certain potential build-up, a more spatially compact charge dipole requires a higher charge and results in a bigger field inside the dipole. This is what happens in the depletion region of a metal-semiconductor junction when the doping level in the semiconductor increases.

It is interesting to realize that Eqs. 7.15 and 7.16 are identical to that of a highly asymmetric P<sup>+</sup>N junction (Eqs. 6.21 and 6.22, respectively). This makes sense as in that case, we learned that the electrostatic potential drops entirely in the lowly doped n-type semiconductor. That is also the case in the metal-semiconductor junction studied here.

Exercise 7.1: Calculate the built-in potential, the depletion-region thickness and the maximum electric field at 300 K of an Al-Si junction with  $q\varphi_{Bn}=0.68$  eV in thermal equilibrium. The doping level of the Si is  $N_D=10^{17}$  cm<sup>-3</sup>.

For  $N_D = 10^{17} \ cm^{-3}$  Si at 300 K, the distance between the conduction band and the Fermi level is  $q\varphi_n = 0.15 \ eV$ . Using Eq. 7.4,  $\phi_{bi}$  is:

$$\phi_{bi} = \varphi_{Bn} - \varphi_n = 0.53 V$$

The depletion region thickness can be obtained from Eq. 7.15:

$$x_d = \sqrt{\frac{2\epsilon\phi_{bi}}{qN_D}} = \sqrt{\frac{2\times1.04\times10^{-12}\ F/cm\times0.53\ V}{1.6\times10^{-19}\ C\times10^{17}\ cm^{-3}}} = 8.3\times10^{-6}\ cm = 83\ nm$$

The maximum electric field occurs at the metal-semiconductor interface. From Eq. 7.16, it is given by:

$$|\mathcal{E}_{o,max}| = \frac{qN_Dx_d}{\epsilon} = \frac{1.6 \times 10^{-19} \ C \times 10^{17} \ cm^{-3} \times 8.3 \times 10^{-6} \ cm}{1.04 \times 10^{-12} \ F/cm} = 1.4 \times 10^5 \ V/cm$$

With the electrostatic potential now completely determined, we are in a position to calculate the equilibrium carrier concentrations and verify our initial assumptions. For this, we use the Boltzmann relations, which for our choice of potential reference are written as:

$$n_o(x) = N_D \exp \frac{q\phi_o(x)}{kT} \tag{7.17}$$

$$p_o(x) = \frac{n_i^2}{N_D} \exp \frac{-q\phi_o(x)}{kT}$$

(7.18)

with  $\phi_o(x)$  given by Eqs. 7.13-7.14.  $n_o(x)$  and  $p_o(x)$  are also sketched in Fig. 7.8.

We can now verify the assumptions that were made in formulating the depletion approximation. First, in going from 7.8 to 7.9, we neglected the equilibrium hole concentration. The location where  $p_o$  is highest, as can be seen in Fig. 7.8, is at the metal-semiconductor interface. At that point,

$$p_o(0) = \frac{n_i^2}{N_D} \exp \frac{q\phi_{bi}}{kT} = N_v \exp \frac{-(E_g - q\varphi_{Bn})}{kT}$$

(7.19)

where we have also used Eqs. 7.4 and 2.39. This equation implies that for  $p_o(0)$  to be negligible next to  $N_D$ ,  $q\phi_{Bn}$  must not get too close to  $E_g$ . As the exercise below shows, for typical doping levels and common metals, this condition is readily satisfied.

We also neglected  $n_o$  next to  $N_D$  everywhere in the depletion region. We must make sure that at the interface,  $n_o$  is sufficiently small for this assumption to hold everywhere else. At x = 0, we have:

$$n_o(0) = N_D \exp \frac{-q\phi_{bi}}{kT} = N_c \exp \frac{-q\varphi_{Bn}}{kT}$$

(7.20)

where we have also used Eqs. 7.4 and 2.39. This condition is satisfied if  $\phi_{Bn}$  is at least several kT/q's.

Exercise 7.2: Specify the range of values of Schottky barrier height that at 300 K allow the use of the depletion approximation in equilibrium for metal-semiconductor junctions built on  $N_D = 10^{17} \text{ cm}^{-3} \text{ Si}$ .

The upper limit of  $q\varphi_{Bn}$  is set by the maximum tolerable  $p_o$  at the metal-semiconductor interface. This is given by Eq. 7.19:

$$p_o(0) = N_v \exp \frac{-(E_g - q\varphi_{Bn})}{kT} \ll N_D$$

Solving for  $q\varphi_{Bn}$ , we get:

$$q\varphi_{Bn} \ll E_g - kT \ln \frac{N_v}{N_D}$$

For  $N_D = 10^{17}~cm^{-3}$  at 300 K, this demands that  $q\varphi_{Bn}$  be a few kT's smaller than 0.98 eV.

The lower limit of  $q\varphi_{Bn}$  is set by the maximum tolerable  $n_o$  at x=0 given by Eq. 7.20:

$$n_o(0) = N_c \exp \frac{-q\varphi_{Bn}}{kT} \ll N_D$$

For  $N_D=10^{17}~cm^{-3}$  at 300 K, this demands that  $q\varphi_{Bn}$  be at least several kT's over 0.15 eV.

Since most metals on Si fall within these two limits, the depletion approximation is of very wide applicability.

## 7.3 Current-voltage characteristics of ideal Schottky diode

When a voltage is applied to the two terminals of a metal-semiconductor junction, current flows. As in the case of the PN diode, the current through a Schottky diode exhibits rectifying behavior. Before we can understand the origin of this, we must study the modifications that the electrostatics of the junction undergo upon the application of a voltage. This is the topic of the next subsection.

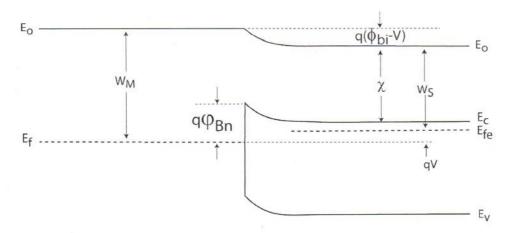

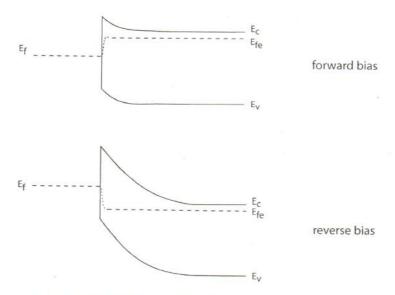

Figure 7.9: Energy band diagram of a metal/n-semiconductor junction in forward bias (V > 0).

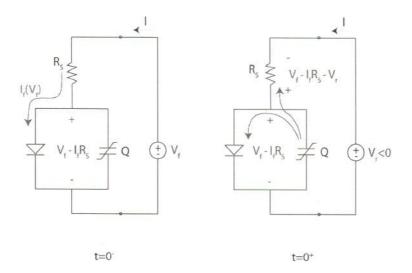

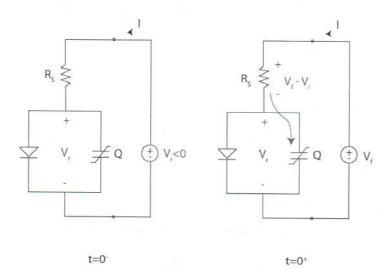

### 7.3.1 Electrostatics under bias

Let us connect a battery with voltage V across a Schottky diode. Through the contact to the Schottky metal, the positive side of the battery "grabs" on the Fermi level in the metal. Through the ohmic contact, as we will see in Section 7.8, the negative side of the battery grabs on the majority carrier quasi-Fermi level of the semiconductor. The application of a voltage V between the Schottky metal and the ohmic contact therefore results in a split between the Fermi level of the metal and the quasi-Fermi level for electrons in the semiconductor of a magnitude qV, as shown in Fig. 7.9 for forward bias and Fig. 7.10 for reverse bias. What is the resulting energy band diagram? Do the electrostatics change across the structure? If so, how do they change?

A complete answer to these questions must be deferred until we have a way to calculate the current that flows when a voltage is applied. This is a chicken and egg problem. We cannot calculate the current without knowing the potential distribution through the structure, which we cannot compute without knowing the currents. To break this circle, let us first assume that the current has a negligible impact on the electrostatics. We will then use this to compute the currents. At that point, we can estimate the order of magnitude of the required corrections and perform them if they are not too large, or ignore them if they are very small.

In the case of a resistor, when a voltage was applied across its terminals, we made the implicit assumption that the voltage dropped in a uniform way along its length. That is why the energy band diagram is tilted with a constant slope everywhere. This is reasonable if the resistor has uniform properties (resistivity and cross section) along its length. In the case of the Schottky diode, the situation is rather different. This structure has basically five rather different regions where the voltage can drop: the Schottky metal bulk, the interface of the Schottky metal with the semiconductor, the space-charge region in the semiconductor, the quasi-neutral region or bulk of the semiconductor and the ohmic contact to the semiconductor. Since the Schottky metal is very conducting in comparison with the semiconductor, the voltage drop there is negligible. At

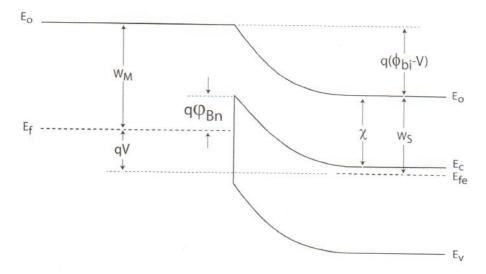

Figure 7.10: Energy band diagram of a metal/n-semiconductor junction in reverse bias (V < 0).

its interface with the semiconductor, the Schottky metal can sustain some electrical charge. This is a very thin region and cannot absorb any significant voltage. Moving into the semiconductor, if we compare the QNR with the SCR, we can see that the QNR has many more carriers than the SCR; the SCR is a lot more "resistive" than the QNR and it is reasonable to assume that most of the voltage drops there. In an ideal Schottky diode, we also neglect the ohmic drop in the ohmic contact. This all leads to assuming in a first pass that the voltage that is applied to a Schottky diode drops entirely across the SCR. We will review this after we discuss the I-V characteristics of the junction.

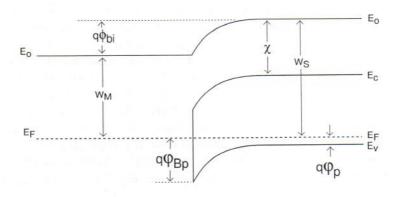

Fig. 7.9 shows the energy band diagram in forward bias. In this case, the quasi-Fermi level for electrons in the QNR of the semiconductor is raised over the Fermi level of the metal by an amount qV. Since we assume that there is no ohmic drop across the QNR in the semiconductor,  $E_{fe}$  remains flat throughout. The difference in the local vacuum level across the structure is reduced from a value of  $q\phi_{bi}$  in equilibrium, to a value  $q(\phi_{bi} - V)$  in forward bias. The total built-in potential has accordingly shrunk from  $\phi_{bi}$  to  $\phi_{bi} - V$ . How can this be accommodated? By reducing the magnitude of the dipole of charge that is set on both sides of the Schottky interface. Since the volume charge density,  $qN_D$ , cannot be changed, the only way to accomplish this is by shrinking the extent of the space-charge region.

In reverse bias, the situation is similar. In this case, the battery lowers the Fermi level in the semiconductor with respect to the Fermi level in the metal. This *increases* the total band bending across the structure to  $q(\phi_{bi}-V)$  (V is negative). In order to accommodate this, the space charge region must widen. The energy band diagram is shown in Fig. 7.10. In both cases, forward and reverse, continuity of the local vacuum potential prevents any changes on the Schottky barrier height as a result of the bias application.

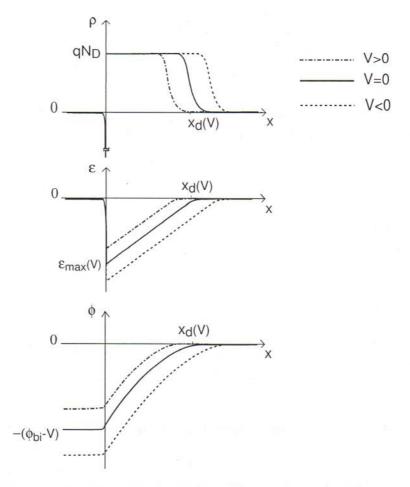

Fig. 7.11 shows the distribution of volume charge density, electric field, and electrostatic po-

Figure 7.11: Sketches of volume charge density, electric field, and electrostatic potential in equilibrium and under bias in a metal/n-semiconductor junction.

tential under forward and reverse bias. The electrostatics are essentially identical to equilibrium, except that the potential difference across the structure is not  $\phi_{bi}$  but  $\phi_{bi} - V$ . This allows us to reuse the solutions to the electrostatics of the equilibrium situation solved above, except where we wrote  $\phi_{bi}$ , we must now write  $\phi_{bi} - V$ . The depletion region thickness is, for example:

$$x_d(V) = \sqrt{\frac{2\epsilon(\phi_{bi} - V)}{qN_D}} = x_d(V = 0)\sqrt{1 - \frac{V}{\phi_{bi}}}$$

(7.21)

The maximum electric field under bias is:

$$|\mathcal{E}_{max}(V)| = \frac{qN_D x_d(V)}{\epsilon} = \sqrt{\frac{2qN_D(\phi_{bi} - V)}{\epsilon}} = |\mathcal{E}_{max}(V = 0)| \sqrt{1 - \frac{V}{\phi_{bi}}}$$

(7.22)

These expressions are valid provided that the depletion approximation continues to apply. This is the case if the forward voltage does not get too close to  $\phi_{bi}$ .

Sketching the carrier concentration distribution and the location of the Fermi level across the structure requires solving the current-voltage characteristics. This is postponed until Section 7.3.3 below.

Exercise 7.3: Calculate the extent of the depletion region and the peak electric field in an Al/n-Si Schottky diode with  $N_D = 10^{17} \text{ cm}^{-3}$  at a forward voltage of 0.5 V at 300K.

We use the results of Exercise 7.1. The built-in potential of this structure is  $\phi_{bi} = 0.53 \ V$ . Then,

$$\sqrt{1 - \frac{V}{\phi_{bi}}} = \sqrt{1 - \frac{0.5 \ V}{0.53 \ V}} = 0.24$$

The extent of the depletion region is:

$$x_d(0.5\ V) = x_d(V = 0)\sqrt{1 - \frac{V}{\phi_{bi}}} = 8.3 \times 10^{-6}\ cm \times 0.24 = 20\ nm$$

The peak electric field is:

$$|\mathcal{E}_{max}(0.5\ V)| = |\mathcal{E}_{max}(V=0)|\sqrt{1 - \frac{V}{\phi_{bi}}} = 1.4 \times 10^5\ V/cm \times 0.24 = 3.4 \times 10^4\ V/cm$$

### 7.3.2 I-V characteristics: qualitative discussion

A Schottky diode is essentially a majority-carrier device. Minority carriers only play a secondary role in its behavior. This is not hard to understand since in equilibrium there is not a significant amount of minority carriers anywhere in the semiconductor that can flow and recombine.

It is not uncommon in semiconductor devices under bias to find that a specific region constitutes the bottleneck to current flow while the rest of the device adapts as needed. In these kinds of situations, the strategy to derive a model for the current-voltage characteristics is to focus on this bottleneck and construct a model for transport there. In a Schottky diode, the lowest concentration of carriers is found in the space-charge region. This is where we will center our attention. Fig. 7.12 qualitatively helps us to consider what happens there.

Fig. 7.12 shows three sketches of energy band diagrams for our Schottky diode in three different situations. In equilibrium, Fig. 7.12a, electrons face an energy barrier of height  $q\varphi_{Bn}$  as they attempt to flow from the metal to the semiconductor or vice versa. The electron flow from the metal to the semiconductor is balanced out by the flow from the semiconductor to the metal. The net flow of electrons across the barrier is zero and the net current is zero.

In forward bias, Fig. 7.12b, the Fermi level on the semiconductor is raised by an amount qV with respect to the Fermi level in the metal. Looking from the point of view of the electrons, the energy barrier facing metal electrons attempting to enter into the semiconductor is  $q\varphi_{Bn}$ ,

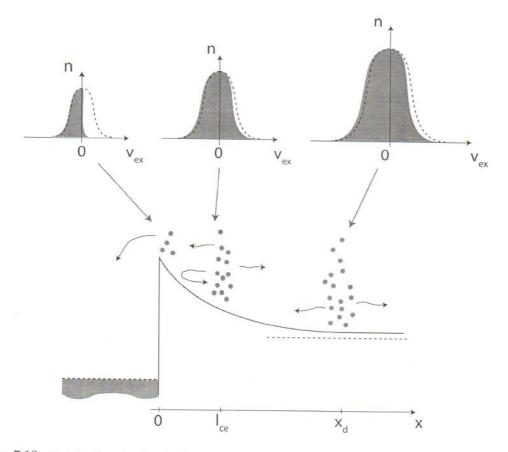

Figure 7.12: Sketch of electron flow across metal-semiconductor junction in a) equilibrium, b) forward bias, and c) reverse bias. In equilibrium there is no net flow of electrons. In forward bias, there is a net flow of electrons from the semiconductor to the metal. In reverse bias, there is net electron flow from the metal to the semiconductor.

just as in equilibrium. In contrast, the energy barrier preventing the flow of electrons from the semiconductor to the metal has decreased to  $q(\varphi_{Bn} - V)$ . Clearly, this results in a net flow of electrons from the semiconductor to the metal producing a current in the contrary sense.

In reverse bias, Fig. 7.12c, the Fermi level on the semiconductor is lowered by an amount qV with respect to the Fermi level in the metal. The energy barrier facing the metal electrons is still unchanged from equilibrium, while the energy barrier in front of semiconductor electrons has now increased to  $q(\varphi_{Bn} - V)$  (V is negative in reverse bias). In consequence, there is a net flow of electrons from the metal to the semiconductor and a current in the contrary sense.

The sketches of Fig. 7.12 also allow us to recognize the functional dependence of the current on the voltage applied across the junction. In forward bias, as V is increased, the number of electrons in the semiconductor that have enough energy to overcome the energy barrier at the Schottky interface increases exponentially with V. This is a consequence of the exponentially

decaying distribution of electrons in the conduction band of the semiconductor. The electron flux from the semiconductor to the metal should therefore increase as  $e^{qV/kT}$ .

In reverse bias, on the other hand, the number of electrons in the semiconductor with enough energy to overcome the interfacial barrier is also exponentially suppressed as the reverse bias |V| increases. When |V| exceeds a few kT/q's, the injection of electrons from the semiconductor to the metal is completely suppressed and the current saturates to the value given by the injection of electrons from the metal to the semiconductor which is unchanged from equilibrium.

Our qualitative arguments have brought us quite far. We have identified the fact that overcoming the energy barrier at the Schottky interface is the bottleneck to electron flow. Thinking in terms of the electron population at that bottleneck qualitatively explains the rectifying behavior of the Schottky diode. We are just a step away from developing a simple model for the current-voltage characteristics. What we are missing is a way to figure out the *rate* at which electrons flow through the SCR.

Let us start by thinking about the situation in thermal equilibrium. With V=0, the net current anywhere is zero. In the SCR, where an electric field is present, that means that there is a drift current that must be perfectly balanced everywhere by a diffusion current. This originates in the gradient of electron concentration that exists from the bulk, where it is highest, to the metal-semiconductor interface where it is lowest.

Under forward bias, the field distribution in the SCR shrinks in magnitude and spatial extent. This breaks the balance of drift and diffusion with diffusion prevailing over drift. This yields a net electron flow from the semiconductor towards the metal. As these electrons enter the metal, they quickly lose their energy thermalizing with the many electrons there. Somehow, what limits the forward bias current is the ability of electrons to reach the metal-semiconductor interface. Once there, they are immediately "sucked" by the metal.

We can contemplate two extreme situations here. In one, the rate limiting step to the current is the process of electron diffusion against the strong electric field in the SCR. In this limit, the electron concentration drops as we advance from the edge of the SCR towards the Schottky interface. At the metal-semiconductor interface, the electron concentration approaches the equilibrium value as these electrons are in a quasi-equilibrium state with those in the metal. A model that describes the current in this limit is known as the drift-diffusion model. This situation is more likely to arise in semiconductors with small mobilities and for low forward bias when the opposing electric field is relatively high.

At the other limit, if the mobility is high and the field is small as a result of strong forward bias, electrons readily reach the metal-semiconductor interface. In this case, it is the process of "emission" into the metal that limits the current. What is exactly this process? We focus at the tip of the energy barrier on the semiconductor side of the the metal-semiconductor interface because that is where the electron concentration is the lowest anywhere in the semiconductor. At that location, the electron concentration is finite and the velocity at which they flow into the metal is also finite. This limits the current to some amount. So, in the limit in which electrons can easily arrive to the Schottky interface from the bulk, it is this maximum "emission current" at the tip of the barrier that sets the diode current. This is known as the thermionic emission model.

As it turns out, for Si, GaAs and many common semiconductors under most conditions, the thermionic emission current is found to be the rate limiting step. This is because the mobilities are high enough and carriers can readily reach the Schottky interface. The next section formulates the thermionic emission model. Appendix AT7.2 describes the drift-diffusion model.

### 7.3.3 I-V characteristics: thermionic emission model

As we have discussed in the previous section, in the thermionic emission model, the current is limited by the electron emission process over the tip of the energy barrier at the Schottky interface. We then focus at the semiconductor side of the Schottky interface located at  $x = 0^+$  and we write the diode current as the net electron current at that location. This is given by the balance between current due to electron flow from the semiconductor to the metal minus the reverse electron flow from the metal to the semiconductor:

$$J_t \simeq J_e(0^+) = J_{e,SM}(0^+) - J_{e,MS}(0^+)$$

(7.23)

In forward bias,  $J_{e,MS}(0^+)$  is very small next to  $J_{e,SM}(0^+)$ . We then neglect this component for the time being and focus on this first term that accounts for electrons emitted from the semiconductor into the metal. This current can be approximately expressed as:

$$J_{e,SM}(0^+) \simeq -qn(0^+)v_e(0^+)$$

(7.24)

Here, the minus sign comes from the fact that with our definition of axis, the velocity of these electrons is against x, or negative  $(J_{e,SM}(0^+))$  ends up positive). Note also that we assume that all electrons at  $x = 0^+$  contribute to this current component. The reverse current is very small and, for the time being, we can ignore the few electrons that support it.

To proceed, we need to exploit the assumption that electrons have no difficulty reaching the Schottky interface from the bulk. This is in essence, the quasi-equilibrium approximation in which electrons across the SCR are all in equilibrium with each other and also with electrons in the bulk of the semiconductor. Without further thinking, the Boltzmann relation would allow us to express  $n(0^+)$  in terms of the electron concentration in the bulk,  $N_D$ , and the difference of potentials between the surface and the bulk,  $\phi_{bi} - V$ . We would be then tempted to write:

$$n(0^{+}) = N_D \exp \frac{-q(\phi_{bi} - V)}{kT}$$

(7.25)

But there is a problem here. At  $x = 0^+$  the electron distribution cannot be close to equilibrium. In fact, it has to be very different from an equilibrium Maxwellian distribution. A carrier distribution can only be considered in thermal equilibrium when electrons undergo many collisions with the lattice that randomize their velocity. Right at the metal-semiconductor interface, any electron that has velocity components pointing towards the metal will be "sucked" by the metal but no electron in the metal can make it into the semiconductor because there is a large

Figure 7.13: Sketch of conduction band across SCR in Schottky diode. Also shown are the distributions of x-component of electron velocity at three locations. Across most of the SCR, electrons are in quasi-equilibrium with the bulk and the electron distribution is Maxwellian. On the semiconductor side of the Schottky interface, the velocity distribution is hemi-maxwellian as only electrons with velocity components pointing towards the metal are present.

energy barrier at the interface that prevents it. So, right at the tip of the barrier at  $x = 0^+$ , there are very few electrons with velocity components pointing towards the semiconductor (this, to the extent that we can neglect  $J_{e,MS}(0^+)$  next to  $J_{e,SM}(0^+)$ ). In effect, at  $x = 0^+$  we have an hemi-maxwellian distribution. This is sketched in Fig. 7.13.

This figure sketches the conduction band diagram of a Schottky diode in forward bias. It also sketches the distribution of the x-component of the electron velocity at three different locations. In the bulk of the semiconductor, there is a large electron concentration that can be considered to be in near thermal equilibrium with the lattice. The distribution of electron concentration in energy and the x component of velocity are very close to perfect equilibrium (dashed lines). Only a small difference exists between the distribution of electron velocities pointing towards the metal and away from the metal that gives rise to a net electron flow towards the Schottky interface. Under the quasi-equilibrium approximation, this situation persists across nearly the entire SCR.

On average, a mean free path away from the metal-semiconductor interface, at  $x = l_{ce}$ , the electrons that ultimately are emitted into the metal suffer their last collision. From there on, those that have enough energy to overcome the energy barrier at the interface and that after their last collision have a component of velocity pointing towards the metal succeed in getting emitted into the metal and contribute to diode current. Those that have the right velocity component but do not have enough energy eventually are reflected by the energy barrier and do not contribute to current. All those that scatter back into the semiconductor also do not contribute to current. The end result is that the distribution of electron velocities right at the Schottky interface at  $x = 0^+$  is very far from thermal equilibrium as only the negative velocity half of the Maxwellian distribution is present.

This understanding allows now to correctly estimate  $n(0^+)$ . We can easily express  $n(0^+)$  in terms of  $n(l_{ce})$ , the electron concentration a mean free path away from the interface. On average, only half of the electrons at  $x = l_{ce}$  have a velocity that points towards the interface. Of those, only a fraction have enough kinetic energy to make it over the potential barrier that exists between x = 0 and  $x = l_{ce}$ . The height of this potential barrier is given by the electrostatic potential difference between  $x = 0^+$  and  $x = l_{ce}$ , that is  $q[\phi(l_{ce}) - \phi(0^+)]$ . Then, the electron concentration at x = 0 can be written as:

$$n(0^{+}) = \frac{n(l_{ce})}{2} \exp \frac{q[\phi(0^{+}) - \phi(l_{ce})]}{kT}$$

(7.26)

The electron concentration at  $x = l_{ce}$  can be computed by solving the drift-diffusion problem across the rest of the SCR. As we have mentioned before, in semiconductors with relatively high mobilities, such as Si and GaAs, a quasi-equilibrium situation prevails over the SCR from the bulk up to  $x = l_{ce}$ . We can then use the Boltzmann relation to relate  $n(l_{ce})$  and  $n(x_d) \simeq N_D$ :

$$n(l_{ce}) \simeq N_D \exp \frac{q\phi(l_{ce})}{kT}$$

(7.27)

We can now substitute 7.27 into 7.26 and use the fact that  $\phi(0^+) = -(\phi_{bi} - V)$  obtained in Section 7.3 to get:

$$n(0^{+}) = \frac{N_D}{2} \exp \frac{-q(\phi_{bi} - V)}{kT} = \frac{N_c}{2} \exp \frac{-q(\varphi_{Bn} - V)}{kT}$$

(7.28)

Equation 7.28 has a simple and intuitive physical interpretation. The electron concentration at  $x=0^+$  is exactly half of what one would have if it was in thermal equilibrium with the bulk (Eq. 7.25). The factor of 1/2 originates from the lack of scattering to the left of x=0 to bring any electrons back. All electrons at  $x=0^+$  are injected into the metal. Notice that, as expected,  $n(0^+) \sim e^{qV/kT}$ .

The second step in the construction of a model for current is the computation of the electron velocity at the interface pointing towards the metal. In Ch. 4 we introduced the notion of thermal velocity of electrons,  $v_{the}$ . This is the average instantaneous velocity of electrons over distances shorter than a mean free path. At the metal-semiconductor interface, however, most electrons

point into the metal with velocities at an angle, therefore contributing a smaller net forward velocity. When the statistics of the electron velocity distribution are properly taken into account, the velocity at which electrons are emitted from the semiconductor into the metal (and vice versa in reverse bias) is actually  $v_{the}/2$ . Using Eq. 4.5, we can then write:

$$v_e(0^+) = -\frac{v_{the}}{2} = -\sqrt{\frac{2kT}{\pi m_{ce}^*}}$$

(7.29)

where the minus sign simply indicates that electrons are flowing in the contrary sense to our choice of axis. For Si at room temperature,  $v_e(0^+)$  is just about  $10^7 \text{ cm/s}$ .

Plugging Eqs. 7.28 and 7.29 into 7.24, we get:

$$J_{e,SM}(0^{+}) = qN_{D}\sqrt{\frac{kT}{2\pi m_{ce}^{*}}} \exp\frac{-q(\phi_{bi} - V)}{kT} = qN_{c}\sqrt{\frac{kT}{2\pi m_{ce}^{*}}} \exp\frac{-q\varphi_{Bn}}{kT} \exp\frac{qV}{kT}$$

(7.30)

where we have used Eq. 7.4 and the relationship given in Ch. 4 between  $\varphi_n$ ,  $N_D$  and  $N_c$ .

Using now the expression for  $N_c$  given in Eq. 2.26, we can write:

$$J_{e,SM}(0^+) = A^*T^2 \exp \frac{-q\varphi_{Bn}}{kT} \exp \frac{qV}{kT}$$

$$(7.31)$$

where  $A^*$  is:

$$A^* = \frac{4\pi q k^2 m_o}{h^3} \sqrt{\frac{(m_{de}^*/m_o)^3}{(m_{ce}^*/m_o)}}$$

(7.32)

$A^*$  is called Richardson's constant and is a characteristic of the material and the type of carrier. The quantity in front of the square root has a value of 120  $A \cdot cm^{-2} \cdot K^{-2}$ .

We have solved half of the problem. We still need to get  $J_{e,MS}(0^+)$  to complete the calculation. However, we know that the current due to electron flow from the metal to the semiconductor is unaffected by the application of a voltage. This is again due to the fact that the energy barrier that is presented to electrons in the metal does not change with bias. Therefore, we can get an expression for  $J_{e,MS}(0^+)$  by equating it to  $J_{e,SM}(0^+)$  in Eq. 7.31 at zero volts when the net current should be zero. This yields:

$$J_{e,MS}(0^+) = A^*T^2 \exp \frac{-q\varphi_{Bn}}{kT}$$

(7.33)

The final net diode current is then:

$$J_t = A^* T^2 \exp \frac{-q\varphi_{Bn}}{kT} (\exp \frac{qV}{kT} - 1)$$

$$(7.34)$$

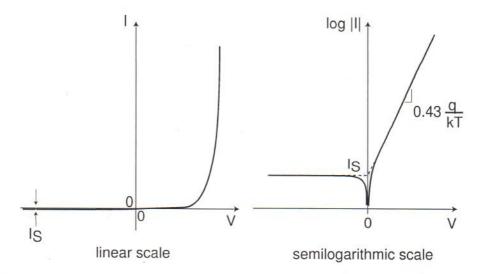

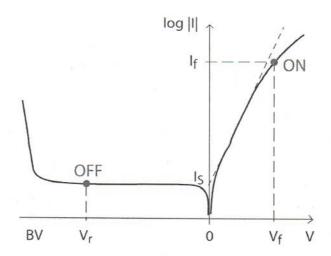

Figure 7.14: Sketch of I - V characteristics of metal-semiconductor junction, in a linear scale on the left, and in a semilogarithmic scale on the right.

This equation is valid in forward as well as in reverse bias since in reverse bias, the current saturates to Eq. 7.33 (with a minus sign) as the forward emission of electrons from the semiconductor to the metal is completely suppressed.

In a diode that has a junction area  $A_j$ , the current flowing through the diode is then:

$$I = I_S(\exp\frac{qV}{kT} - 1) \tag{7.35}$$

where  $I_S$  is called the *saturation current*. This is identical to a PN diode and is plotted again in Fig. 7.14 in linear and semilog scales. In a semilog scale, the forward bias current appears as a straight line with a slope of  $(q/kT) \log e = 0.43q/kT$  or  $60 \ mV/dec$  at room temperature.

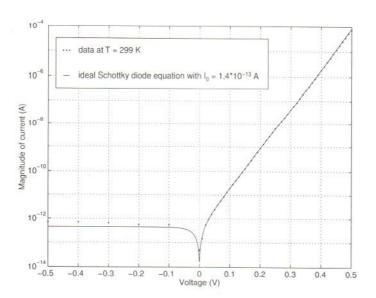

Fig. 7.15 shows experimental I-V characteristics of a PtSi/n-Si junction. The experimental data follows the shape predicted by Eq. 7.35 very accurately.

The saturation current  $I_S$  has a very peculiar set of dependencies in itself:

$$I_S = A_j A^* T^2 \exp \frac{-q\varphi_{Bn}}{kT} \tag{7.36}$$

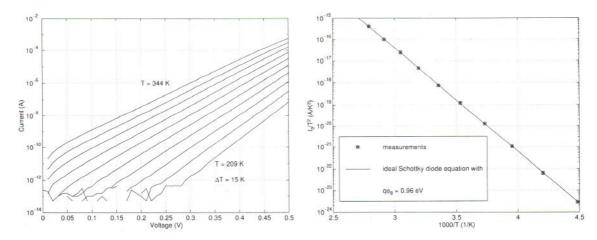

$I_S$  in this equation depends exponentially with a minus sign on the Schottky barrier height. This is reasonable since the higher the barrier, the lower (exponentially) the flow of electrons over it. The pre-exponential factor depends on the square of the absolute temperature. Since  $A^*$  does not depend on temperature,  $I_S/T^2$  is thermally activated with an activation energy equal to  $q\varphi_{Bn}$ . This suggests an experimental procedure to determine  $q\varphi_{Bn}$ . First, I-V characteristics are measured as a function of temperature and  $I_S$  is extracted at all temperatures. Then  $I_S/T^2$  is graphed in an Arrhenius plot. The slope of the resulting straight line gives  $q\varphi_{Bn}$ . This is

Figure 7.15: Experimental I-V characteristics of PtSi/n-Si Schottky diodes at room temperature [diode courtesy of B. Scharf (Analog Devices), data and model courtesy of S. Krupenin (MIT)].

experimentally illustrated in Fig. 7.16 for the same diode of Fig. 7.15.

A word about Richardson constant  $A^*$ . As seen in Eq. 7.32, the thermionic emission theory predicts it to depend only on the semiconductor and to be independent of the metal. For n-Si, if one plugs in the appropriate values of effective masses, one obtains  $A^* \simeq 258 \ A \cdot cm^{-2} \cdot K^{-2}$ . A more refined theory predicts that  $A^*$  depends somehow on the crystalline orientation of the material. It is not the same to make a Schotky diode on (100) Si than on (111) Si. In practice, one can experimentally extract  $A^*$  from actual measurements on Schottky diodes. What is found is that  $A^*$  depends a lot on the nature of the metal itself, its thickness, and the details of the process: surface preparation prior to metal deposition, the deposition parameters and any post-deposition treatments. The reasons for these dependencies are various: surface roughness, local strain, the formation of metal-semiconductor compounds, interfacial oxides, etc. The bottom line is that for a given metal-semiconductor system, we cannot simply take the theoretically predicted value of  $A^*$  given by the thermionic emission theory and expect to accurately predict  $I_S$  in Schottky diodes. The proper action is to build some test diodes and measure  $A^*$  and then use this in the model.

Let us now discuss the key assumption that we have made in the development of our theory. In deriving the previous equations, we assumed that thermionic emission of electrons over the Schottky barrier is the rate-limiting mechanism for electron transport, and that drift and diffusion through the SCR are in near perfect balance from  $x = l_{ce}$  to the end of the depletion region towards the body. This assumption allowed us to focus on the emission process over the tip of the energy barrier at the metal-semiconductor interface in order to compute the current. Elsewhere in the SCR, we used the Boltzmann relation to calculate the electron concentration.

For this quasi-equilibrium assumption to apply, the net current that flows through the junction

Figure 7.16: Left: Forward I-V characteristics of PtSi/n-Si Schottky diode for different temperatures. Right: Arrhenius plot of  $I_S/T^2$  for the same diode. The slope of the straight line gives  $q\varphi_{Bn}$  [diode courtesy of B. Scharf (Analog Devices), data and fit courtesy of S. Krupenin (MIT)].

must be much smaller than either the drift or the diffusion currents. In this way, only a small imbalance between these two currents needs to exist. It is particularly intuitive to focus on the drift current. Quasi-equilibrium is guaranteed up to  $x = l_{ce}$  if the thermionic emission current is much smaller than the drift current at that location, that is,

$$|J_{e,SM}(0^+)| \ll |J_{e,drift}(l_{ce})|$$

(7.37)

Using Eqs. 7.24, 7.26 and 7.29 on the left hand side, and the usual expression for the drift current on the right hand side  $(J_{e,drift} = q\mu_e n\mathcal{E})$ , we can rewrite this as:

$$\frac{1}{4}v_{the}\exp(-\frac{q\Delta\phi_{lce}}{kT}) \ll \mu_e|\mathcal{E}(l_{ce})| \tag{7.38}$$

where we have defined  $\Delta \phi_{lce}$  as the potential build-up over the first mean-free path of the SCR starting from the metal-semiconductor interface.

Expressions 4.5, 4.8 and 4.10 allow us to express the mobility in terms of the velocity and the mean free path as:  $\mu_e = ql_{ce}/(m_{ce}^*v_{the})$ . Plugging this on the right hand side of Eq. 7.38, and noting that  $l_{ce}|\mathcal{E}(l_{ce})| < \Delta \phi_{lce}$ , we can rewrite this expression as:

$$\frac{q\Delta\phi_{lce}}{kT} \exp(\frac{q\Delta\phi_{lce}}{kT}) \gg \frac{2}{\pi}$$

(7.39)

This is readily satisfied if:

$$\Delta \phi_{lce} > 1.5 \frac{kT}{q} \tag{7.40}$$

Figure 7.17: Energy band diagrams in metal-semiconductor junction in forward and reverse bias showing the location of the quasi-Fermi level for electrons.

or, in other words, if the potential drop in the first mean free path from the interface exceeds 1.5kT/q. This is called the *Bethe condition*. In Si this condition is easy to satisfy at all practical voltages because the mean-free paths are rather long. An example is given in Exercise 7.4.

Exercise 7.4: Evaluate the validity of the Bethe condition for an Al/n-Si Schottky diode with  $N_D = 10^{17} \text{ cm}^{-3}$  at a forward voltage of 0.5 V at 300K.

For this calculation, we need the mean free path in the SCR. If we assume that the electron mobility in an SCR is identical to that of a QNR with an identical doping level, we can use the result of Exercise 4.1 where we obtained for this same doping level  $l_{ce} \simeq 22 \ nm$ .

From Exercise 7.3 we know that for this Schottky diode at this forward voltage, the peak field at the Schottky interface is  $|\mathcal{E}_{max}| \simeq 3.4 \times 10^4 \ V/cm$ . Then, the potential drop in the first mean free path away from the Schottky interface is:

$$\Delta\phi_{lce} \simeq l_{ce} |\mathcal{E}_{max}| \simeq 22 \times 10^{-7}~cm \times 3.4 \times 10^4~V/cm = 0.075~V$$

This is comfortably bigger than  $1.5kT/q \simeq 39$  meV and the Bethe condition is fulfilled. For this Schottky diode, even for such a high forward voltage, the thermionic emission model is the appropriate one.

We are finally in a position to draw the electron quasi-Fermi level,  $E_{fe}$ , across the device. Discussion of the hole quasi-Fermi level still needs to be postponed until we discuss the behavior of minority carriers. Drawing  $E_{fe}$  is now easy. The assumption of quasi-equilibrium across the entire device with the exception of the very first mean-free path implies that the quasi-Fermi level for electrons is flat in this entire region. It location is set by the doping level in the QNR. This is sketched in Fig. 7.17.

Within the very first mean-free path away from the metal-semiconductor interface, the concept

of quasi-Fermi level is not appropriate as the electron distribution is very far from Maxwellian. We indicate this in Fig. 7.17 by means of a dotted line that suggests that the electron distribution comes to equilibrium with the electrons in the metal at the metal-semiconductor interface.

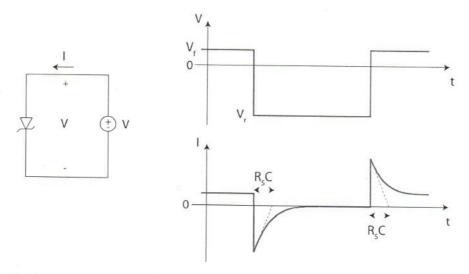

### 7.4 Charge-voltage characteristics of ideal Schottky diode

As we learned in the PN diode, in order to describe the dynamic behavior of a Schottky diode in a circuit, we need a model for the stored charge. If the voltage across the diode changes, the stored charge must change too and the outside circuit must deliver it. This is a real current that needs to be accounted for.

The ideal Schottky diode is a majority carrier device. The current that flows upon the application of a voltage arises from the flow of majority carriers over the energy barrier at the metal-semiconductor interface. In an ideal Schottky diode, unlike a PN diode, the minority carrier concentration is unperturbed from its equilibrium value. There is then no minority carrier storage to contend with. In an ideal Schottky diode, the only stored charge to keep track of is that of the space-charge region which thickness is modulated with the applied voltage as we discussed in Sec. 7.3.1.

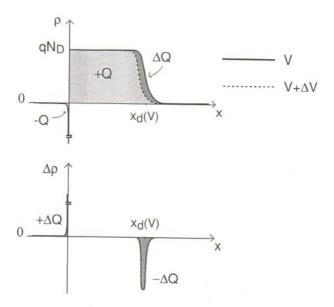

The situation is similar to that of a PN diode. Fig. 7.18 sketches the volume charge density in the space-charge region of a Schottky diode with a certain voltage V applied. Whether the voltage is forward or reverse, there is a dipole of charge of a magnitude Q across the metal-semiconductor interface. For the example depicted in Fig. 7.18, there is a charge +Q in the SCR of the semiconductor that is imaged in an equal amount of charge -Q due to a pile up of electrons at the metal surface.

If the voltage that is applied across the diode is increased (made more positive) by a small amount,  $\Delta V$ , the SCR shrinks a small amount and the pile up of electrons at the metal surface is also reduced somehow. This means that a small quantity of positive charge,  $+\Delta Q$ , is delivered to the metal (the positive plate) and the same amount of negative charge,  $-\Delta Q$ , is delivered to the semiconductor (the negative plate). The overall charge dipole shrinks, as required.

The stored charge in the SCR can easily be obtained within the depletion approximation. From Eq. 7.21, we have:

$$Q(V) = -AqN_D x_d(V) = -A\sqrt{2qN_D \epsilon(\phi_{bi} - V)}$$

(7.41)

As for the PN diode, this equation can be rewritten as:

$$Q(V) = Q(V=0)\sqrt{1 - \frac{V}{\phi_{bi}}}$$

(7.42)

It should not be surprising that we obtain an identical Q - V relationship for the Schottky diode and the PN diode. Essentially, the electrostatics of the SCR for both devices is identical.

Figure 7.18: Change in the volume charge density in a metal/n-semiconductor junction as a result of increasing the voltage across.

The graph of Q vs. V for the PN diode of Fig. 6.21 applies here.

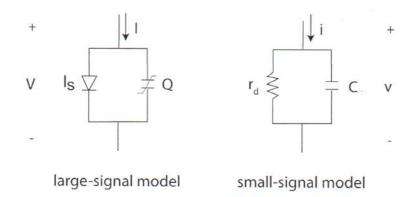

### 7.5 Equivalent circuit models for the ideal Schottky diode

A device equivalent circuit model is a circuit-like description of its electrical behavior. With the physics of the Schottky diode and the PN diode related in so many ways, their equivalent circuit models are also bound to be very close. In fact, topologically, the equivalent circuit models for these two devices are identical.

We studied the equivalent circuit models for the ideal PN diode in Sec. 6.5. We saw that the large-signal ideal PN diode model contains a "charge-less" ideal diode element that embodies its rectifying I-V characteristics plus a charge storage element in parallel that represents the SCR and the minority carrier charge. The equivalent circuit model for the Schottky diode should look exactly the same except for the absence of the minority carrier charge in the charge storage element. For convenience, we graph it again on the left of Fig. 7.19. In this figure  $I_S$  represents the saturation current of the Schottky diode (Eq. 7.36) and Q represents the SCR charge given in Eq. 7.42.

When we discussed the PN diode equivalent circuit models, we also noted the interest in developing a small-signal model that represents in a circuit form the behavior of the device to small excursions around a bias point. For the PN diode, the ideal-diode element is linearized into a resistor and the charge storage element turns into a capacitor. The small-signal equivalent circuit model for an ideal Schottky diode is identical. As graphed on the right of Fig. 7.19, it contains a resistor in parallel with a capacitor. The small-signal resistor is given by an identical

Figure 7.19: Large-signal and small-signal equivalent circuit models for the Schottky diode.

expression to that of the PN diode, reproduced here for convenience:

$$r_d = \frac{kT}{q(I+I_S)} \simeq \frac{kT}{qI} \tag{7.43}$$

where the approximation applies for moderate and strong forward bias. This is the dynamic resistance of the ideal Schottky diode.

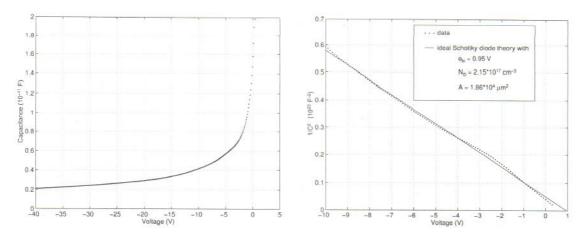

The capacitor is associated with SCR charge storage. As in the case of the PN diode, we can obtain it by differentiating Eq. 7.41 or Eq. 7.42 with respect to voltage:

$$C(V) = A\sqrt{\frac{\epsilon q N_D}{2(\phi_{bi} - V)}} = \frac{C(V = 0)}{\sqrt{1 - \frac{V}{\phi_{bi}}}}$$

(7.44)

This is an identical functional expression to that of a PN diode (sketched in Fig. 6.25). As in that case, this expression for the SCR capacitance can also be obtained in analogy with a parallel plate capacitor by using  $C(V) = A\epsilon/x_d(V)$  and then using Eq. 7.21.

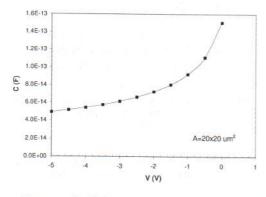

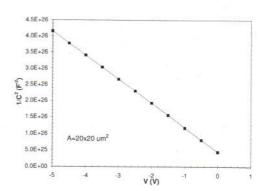

Also in a close parallelism with a strongly asymmetric PN diode, the inverse square of C(V) in Eq. 7.44 is linearly proportional to  $N_D$ , the doping level in the semiconductor. This is a standard way to measure this plus the Schottky barrier height in Schottky diodes, as shown in the example of Fig. 7.20.

### 7.6 Non-ideal and second order effects

In this section we chip away at the long list of assumptions that was made in the definition of the ideal Schottky diode and discuss some important non idealities and second-order effects.

Figure 7.20: C vs. V and  $1/C^2$  vs. V for a GaN Schottky diode [diode courtesy of R. J. Molnar (MIT Lincoln Laboratory), data and fit courtesy of S. Krupenin (MIT)].

#### 7.6.1 Series resistance

In our analysis of the ideal Schottky diode of Fig. 7.2 we neglected the presence of any series resistance. When we derived the expressions for the I-V characteristics, we assumed that the entire voltage applied to the terminals of the device appears across the SCR. But we know that there are ohmic drops at the bottom contact of the diode and in the quasi-neutral body of the device. Just like in the PN diode, these ohmic drops can affect the I-V characteristics of the device at high currents in a significant way.

Since the I-V characteristics of the Schottky diode are functionally identical to those of the PN diode, the role of series resistance is also the same in both devices. We refer to Eq. 6.86 for a modified diode equation that incorporates series resistance, and to Fig. 6.32 for a manifestation of the series resistance in its I-V characteristics. Series resistance is also captured in an equivalent circuit model of the Schottky diode in the same way as for the PN diode (see Fig. 6.33).

There are two components to the series resistance of the Schottky diode: the contact resistance and the body resistance. Between the bottom metal and the semiconductor, there is a contact resistance. We study the physics of ohmic contacts in detail later on in this chapter. As we discussed in the context of the PN diode, a metal-semiconductor contact resistance is characterized through its contact resistivity,  $\rho_c$ . The contact resistance is given by the product of  $\rho_c$  and the area of the contact. Therefore, for the Schottky diode of Fig. 7.2, we have:

$$R_c = \frac{\rho_c}{A} \tag{7.45}$$

Then there is the resistance of the body. This is associated with the QNR as majority carrier electrons drift through this region to support the diode current. The resistance is simply the geometrical resistance of this region given by:

$$R_n = \frac{1}{A} \frac{w_n - x_d}{q \mu_e N_D} \tag{7.46}$$

The voltage dependence of  $R_n$  through that of  $x_d$  is generally negligible. The total resistance of the diode is given by the sum of  $R_c$  and  $R_n$ .

Schottky diodes are frequently utilized in applications in which it is important to minimize any parasitic ohmic drop as this adds to power dissipation. In high frequency applications,  $R_s$  degrades the dynamic response of the diodes, as we will discuss in Section AT7.4. For these reasons, a key consideration in Schottky diode design is to minimize series resistance.

### 7.6.2 Breakdown voltage

In a Shottky diode in reverse bias, a small trickle current flows due to electrons in the metal that have enough energy to overcome the Schottky barrier height at the metal-semiconductor interface and get injected into the semiconductor. As the reverse voltage increases, the magnitude of the electric field in the depletion region increases too. For sufficiently high reverse bias, the flowing electrons might gain enough energy from the electric field and suffer impact ionizing collisions as they travel through the depletion region. The additional carriers that are generated contribute to the total current which in this way increases over the ideal value given by Eq. 7.36 above. For high enough reverse bias, avalanche breakdown might take place and the current increases abruptly to very high values. The manifestation of breakdown in the I-V characteristics of a Schottky diode is similar to that of a PN diode (Fig. 6.34). The voltage at which avalanche breakdown occurs is the breakdown voltage of the device. This is a very important parameter since it limits the highest reverse bias that the device can support.

As in so many other aspects, the physics of avalanche breakdown in Schottky diodes and PN diodes are closely related. So, in principle, we could use the theory presented in Sec. 6.6.4 to model the breakdown voltage of a Schottky diode. From our study of PN diode breakdown, we would then conclude that the breakdown voltage in a Schottky diode is mostly set by the doping level of the semiconductor and should be rather independent of the metal that is used. We can also expect that the higher the doping in the semiconductor, the lower the breakdown voltage.

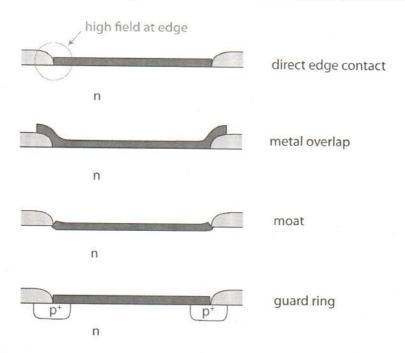

In practice what is found is that for the same doping level in the semiconductor, the breakdown voltage of a Schottky diode is significantly smaller than what is typically obtained in a PN diode. The reason for this has to do with the presence of a high electric field at the sharp edges of the metal that leads to premature breakdown. The situation is illustrated in Fig. 7.21. This problem does not exist in PN diodes because the high field region is inside the semiconductor and away from the metal contacts.

Several solutions to this problem are sketched in Fig. 7.21. One of them relies on the *metal* overlap over an  $SiO_2$  window that defines the active area of the diode. The edges of the metal in this way are not in direct contact with the semiconductor. A most structure sometimes is feasible in certain processes. In this approach, as shown, the semiconductor is slightly etched in the active area of the diode. The curvature of the periphery of the most smoothes out the electric field from the edge of the metal.

Figure 7.21: A direct overlap of the metal edge and the semiconductor results in high electric fields at the corner that lead to premature reverse breakdown (top). This can be mitigated through the use of a metal/oxide overlap, a moat, or a p-n junction guard ring.

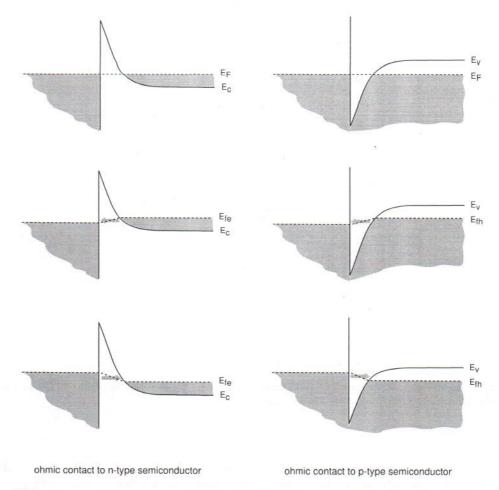

A p-n junction guard ring is also effective. In a design on an n-type well, a p-region is inserted right underneath the periphery of the diode, as sketched in Fig. 7.21. At the edges of the metal, this produces a PN junction in parallel with the Schottky junction. This combination can support a higher reverse voltage. This approach has the drawback of the extra space needed in the lateral dimension by the p-region. This makes the diode bigger and in consequence less attractive economically. There is also the danger in this design that the p-n junction might turn on in forward bias. If that happens, the minority carrier charge associated with the p-n diode considerably slows down the combined device. This can occur, in particular, if a metal with a high Schottky barrier height is being used. Careful design of the p-doping level is required to avoid this problem. This is typically done using a device CAD tool since the problem is intrinsically two-dimensional.

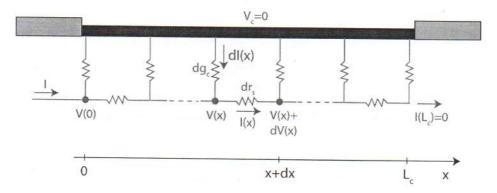

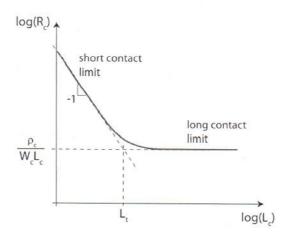

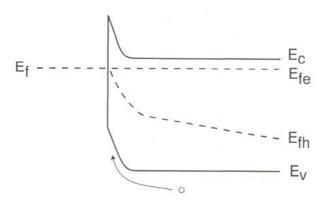

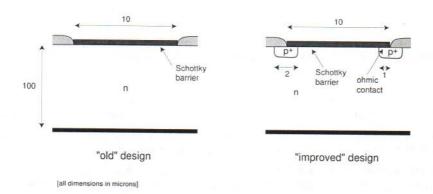

### 7.7 Integrated Schottky diode